Questões de Tecnologia da Informação - Organização e arquitetura de computadores - Arquiteturas e famílias de processadores

Limpar pesquisa

Questão: 61 de 148

64678

Banca: FCC

Órgão: MPE/RN

Cargo(s): Analista do Ministério Público Estadual - Suporte Técnico - Tecnologia da Informação

Ano: 2012

Matéria/Assunto: Tecnologia da Informação > Organização e arquitetura de computadores / Arquiteturas e famílias de processadores

Combinam dois ou mais processadores (chamados núcleos – core) em uma ou mais peças de silício (chamada pastilhas – die).

No Intel Core Duo, todos os núcleos compartilham a mesma cache L1. Cada núcleo tem a sua própria cache L2 dedicada de 2 MB.

Apesar de possuírem vários núcleos os chips multicore atuais não incluem cache L2 e L3.

Normalmente, cada núcleo consiste de todos os componentes de um processador independente, como registradores, ALU, hardware de pipeline e unidade de controle, mais caches L1 de dados e de instruções.

O Intel Core i7 implementa sete processadores x86 SMT, cada um com uma cache L2 compartilhada e com uma cache L3 dedicada.

Questão: 62 de 148

60029

Banca: FCC

Órgão: METRÔ/SP

Cargo(s): Analista Desenvolvimento Gestão Júnior - Ciências da Computação

Ano: 2012

Matéria/Assunto: Tecnologia da Informação > Organização e arquitetura de computadores / Arquiteturas e famílias de processadores

O gerenciamento de energia é feito por meio de um termômetro analógico compartilhado pelos dois núcleos. Os dados lidos por este termômetro são monitorados pelo sistema operacional.

Ambos os núcleos podem ser definidos como uma única zona térmica. Se a temperatura em um núcleo excede o limite, a unidade de controle térmica aumenta a taxa de clock para reduzir a geração de calor.

Ambos os núcleos compartilham a mesma cache L1, mas há uma cache L3 dedicada exclusivamente a cada núcleo. A cache L3 não pode ser compartilhada.

O chip Core Duo inclui uma cache L2 compartilhada. A lógica da cache permite alocação dinâmica do espaço da cache com base nas necessidades atuais do núcleo, de tal forma que a um núcleo possa ser atribuído até 100% de cache L2.

Possui dois Advanced Programmable Interrupt Controller (APIC). O primeiro é destinado a permitir que um núcleo interrompa o processamento do outro. O segundo é destinado ao monitoramento das interrupções de E/S. Cada APIC inclui um temporizador que pode ser ajustado apenas por hardware.

Questão: 63 de 148

59833

Banca: FCC

Órgão: ARCE

Cargo(s): Analista de Regulação - Analista de Sistemas

Ano: 2012

Matéria/Assunto: Tecnologia da Informação > Organização e arquitetura de computadores / Arquiteturas e famílias de processadores

o microprocessador pode executar operações matemáticas como adição, subtração, multiplicação e divisão, utilizando sua UC (Unidade de Controle).

os processadores que podem executar operações extremamente sofisticadas com números grandes em ponto flutuante são destinados apenas aos mainframes.

um microprocessador, ao começar a funcionar, executa primeiro as instruções contidas na RAM, um dispositivo eletrônico que realiza testes no hardware.

os processadores da família Sandy Bridge serão fabricados em 22nm. Quanto maior esse número, maior o número de transistores existentes no processador.

muitos processadores modernos possuem múltiplos decodificadores de instrução, cada um com seu próprio pipeline, permitindo múltiplos canais de execução de instruções.

Questão: 64 de 148

57426

Banca: CESPE / Cebraspe

Órgão: INSS

Cargo(s): Analista do Seguro Social - Engenharia de Telecomunicações

Ano: 2008

Matéria/Assunto: Tecnologia da Informação > Organização e arquitetura de computadores

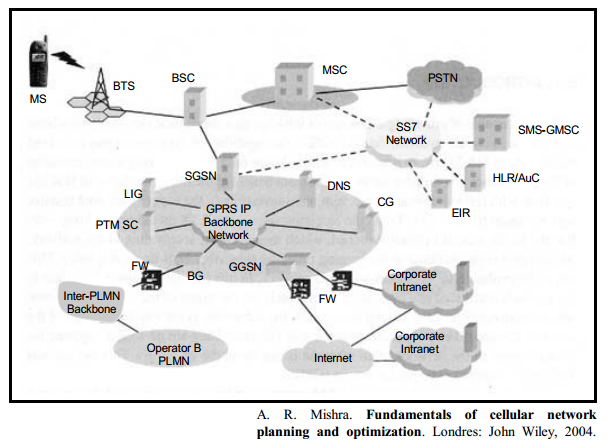

A figura acima ilustra elementos da arquitetura de uma rede GSM

com recursos GPRS, em que a nomenclatura utilizada segue o

estabelecido no 3GPP (3rd Generation Partnership Project). Considerando essa arquitetura, julgue os itens seguintes, relativos ao

planejamento e à otimização de redes GSM/GPRS.

Questão: 65 de 148

57447

Banca: CESPE / Cebraspe

Órgão: INSS

Cargo(s): Analista do Seguro Social - Engenharia de Telecomunicações

Ano: 2008

Matéria/Assunto: Tecnologia da Informação > Organização e arquitetura de computadores

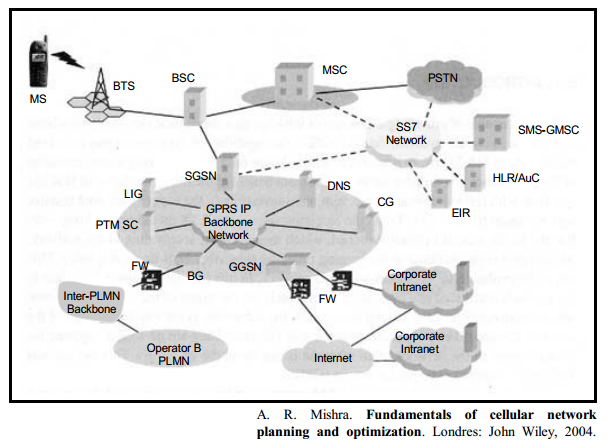

A figura acima ilustra elementos da arquitetura de uma rede GSM

com recursos GPRS, em que a nomenclatura utilizada segue o

estabelecido no 3GPP (3rd Generation Partnership Project). Considerando essa arquitetura, julgue os itens seguintes, relativos ao

planejamento e à otimização de redes GSM/GPRS.